전체 회원 중 상위 0.1% 권위

10년 이상 경험, 연구개발 성과

송 부사장, 업계 최초 5G 모뎀 개발

한 상무, 차세대 3D D램 개발 주도

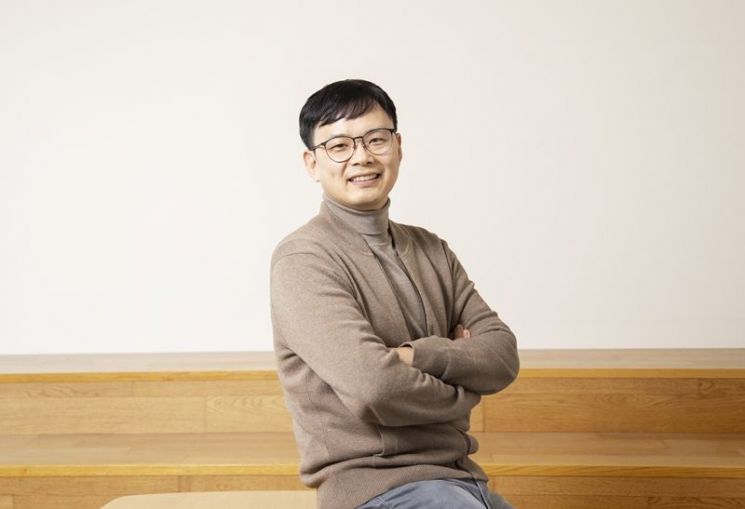

삼성전자 반도체(DS)부문 DSRA(미주 반도체연구소) 시스템LSI 연구소를 총괄하는 송기봉 부사장과 한진우 반도체연구소 디램(DRAM) TD팀 상무가 세계 최대 규모의 전기·전자·컴퓨터·통신 분야 학회인 미국 전기전자공학회(IEEE)의 2026년 펠로우(석학회원)로 선정됐다.

22일 삼성전자 뉴스룸에 따르면 'IEEE 펠로우'는 미국 전기전자공학회가 회원에게 부여하는 최고 명예 등급으로, 전체 회원의 상위 0.1%만 오를 수 있는 권위 있는 자격이다. 전기·전자공학 전반에서 10년 이상 경험을 쌓고, 통신·반도체 등 다양한 분야에서 탁월한 연구개발 성과를 통해 산업과 사회 발전에 기여한 인물을 대상으로 매년 IEEE 이사회가 엄정한 기준에 따라 선정한다.

글로벌 빅테크 기업들을 거쳐 삼성전자 미주 반도체연구소에 합류한 송 부사장은 현재 시스템LSI 미주 연구소를 총괄하며 모뎀, 커넥티비티(Connectivity), 온디바이스 AI(On-device AI), 시스템 온 칩(SoC) 기술 개발을 이끌고 있다. 현재까지 무선통신, 신호처리, 모뎀-RF 시스템을 위한 AI 기술 등과 관련해 다수의 연구 논문을 발표했으며, 80건이 넘는 특허를 보유하고 있다.

송 부사장의 펠로우 선정에는 그가 오랜 기간 셀룰러 통신 분야에서 축적해 온 모뎀-RF 시스템 설계 및 성능 최적화 기여가 주요하게 반영됐다. 업계 최초 5G 모뎀 개발과 5G mmWave(밀리미터파) 송수신기 기술 고도화, 엑시노스 모뎀 5400과 엑시노스 2500에 적용된 비지상 네트워크(NTN) 기술 기반 '위성 응급 서비스(Satellite SOS)' 구현 등 차세대 이동통신 기술의 상용화를 이끈 성과가 높게 평가된 것이다.

미 항공우주국을 거쳐 삼성전자에 합류한 한 상무는 200건 이상의 특허와 160편 이상의 SCI(우수 학술지)급 논문을 발표하며, 메모리, 로직, 센서 등 다양한 분야에서 연구 성과를 쌓아왔다. 그는 차세대 3D D램 개발 공로와 그동안의 연구 성과를 인정받아 2026년 IEEE 펠로우로 선정됐다.

한 상무는 반도체 미세화 한계를 극복하기 위해 '차세대 3D D램' 연구를 선도하며, 새로운 메모리 구조의 가능성을 탐구해 왔다. D램 셀을 평면이 아닌, 수직 방향으로 쌓아 칩 면적당 저장 용량을 확장하는 이 접근법은 차세대 메모리 기술의 핵심으로 주목받고 있다. 삼성전자 DS부문 반도체연구소에서 차세대 D램 연구 조직을 담당하고 있는 그는 3차원 구조를 메모리 셀에 적용하는 D램 개발을 주도하고 있다.

송 부사장은 "6G와 피지컬 AI 시대에는 수많은 머신과 센서가 생성하는 데이터가 서로 상호작용하게 될 것"이라며 "이러한 환경에 맞춰 통신, 연산, 센싱(Sensing)이 만나는 지점을 중심으로 새로운 반도체 기술과 제품을 창출하고, 미래 혁신을 주도해 나가고자 한다"고 밝혔다.

한 상무도 "우리나라 반도체 산업은 범용 제품 중심의 경쟁력으로 성장하며, 글로벌 최고 수준의 위상을 구축해 왔다"며 "그러나 글로벌 공급망 재편과 기술 패권 경쟁 등으로 반도체 생태계가 빠르게 변화하고 있어 위기와 기회가 공존하는 시점"이라고 평가했다.

지금 뜨는 뉴스

이어 "현장에서도 맞춤형 스페셜티(Specialty) 제품의 수요가 꾸준히 늘어나는 만큼, 연구자들은 수평적으로 다양한 연관 기술을 이해하고 연결하는 역량과 함께, 수직적으로는 제품 구조와 계층 관계에 대한 깊은 이해를 갖추는 것이 중요하다"며 "기술을 넓게 바라보고, 국제적 네트워크를 구축해 협력할 수 있는 우호적 연구 생태계를 만드는 것 역시 앞으로의 경쟁력에 큰 도움이 될 것"이라고 밝혔다.

박준이 기자 giver@asiae.co.kr

<ⓒ투자가를 위한 경제콘텐츠 플랫폼, 아시아경제(www.asiae.co.kr) 무단전재 배포금지>

![전문가 4인이 말하는 '의료 생태계의 대전환'[비대면진료의 미래⑥]](https://cwcontent.asiae.co.kr/asiaresize/319/2026013014211022823_1769750471.png)

![같은 매장인데 할인은 두 배 차이?…통신사 멤버십의 '이중 구조' [혜택의 정석]](https://cwcontent.asiae.co.kr/asiaresize/308/2026021207130939233_1770847989.jpg)

![휴게소 가서 화장실만?…차 세우게 만드는 이유가 있네[디깅 트래블]](https://cwcontent.asiae.co.kr/asiaresize/308/2026021517185743202_1771143536.jpg)