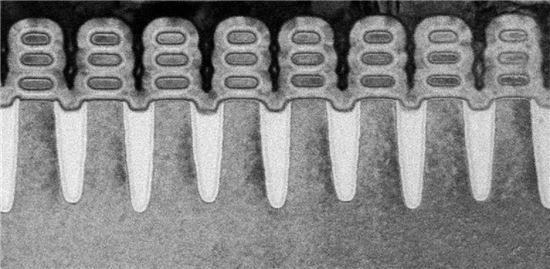

IBM '5나노 트랜지스터' 개발

5나노 칩 개발 가능성 높여

현재 10나노칩과 비교해

동일 전력시 성능 40% 향상

7나노급 테스트 성공 후 2년만

IBM이 손톱만한 크기의 칩에 300억개의 트랜지스터를 집적할 수 있는 '5나노 트랜지스터' 기술 개발에 성공했다. 이에 따라 더 강력한 성능의 5나노 칩 생산이 머지 않은 미래에 가능할 것으로 전망된다.

5나노칩이 상용화되면 전력 효율성이 개선돼 스마트폰과 기타 모바일 제품의 배터리 지속시간이 현재 사용되는 기기들과 비교해 최대 2~3배 늘어나게 된다.

5일 IBM은 "삼성전자 등 글로벌 파운드리와 함께 업계 최초로 5나노미터칩 제조가 가능한 실리콘 나노시트(nanosheet) 트랜지스터 생산 공정 개발에 성공했다"고 밝혔다. 삼성전자, 글로벌 파운드리가 함께하는 IBM 리서치 연합(IBM Research Alliance)이 200억개의 트랜지스터를 집적할 수 있는 7나노 테스트노드칩 개발에 성공한지 불과 2년도 지나지 않은 시점이다.

현재 시장에서 사용되고 있는 최신 10나노 칩과 비교했을 때, 나노시트 기반의 5나노 기술을 사용하면 동일한 전력 소모 시 성능이 40% 향상되고, 동일한 성능에서는 전력 소모량이 75% 감소한다. 이러한 발전을 통해 인공지능(AI) 시스템과 가상 현실, 그리고 모바일 디바이스에 대한 미래의 요구사항을 더 빠르게 충족시킬 수 있을 전망이다.

이에 따라 클라우드를 통해 제공되는 인공지능을 포함한 코그너티브(인지) 컴퓨팅, 사물인터넷(IoT)및 기타 데이터 집약적 애플리케이션의 성능 향상으로 이어져 이 기술들의 발전이 가속화될 것으로 보인다.

IBM 리서치는 나노시트 반도체 기술에 대한 연구를 10년 이상 진행했다. 이번 연구를 통해 업계 최초로 핀펫 아키텍처보다 우수한 전기적 특성을 가진적층 나노시트 디바이스를 설계하고제조할 수 있음을 입증했다.

7나노 테스트 노드와 200억개 트랜지스터를 제작하는데 사용된 극자외선(Extreme Ultraviolet, EUV) 리소그래피 기술이 이번 나노시트 트랜지스터 아키텍처에도 적용됐다. 이 기술을 통해 단일 제조 공정이나 칩 설계상에서 나노시트 너비를 지속적으로 조정할 수 있다.

이로써 기존의 핀펫 트랜지스터 아키텍처에서는 전류가 흐르는 핀높이의 제약 때문에 불가능했던 특정 서킷의 성능과 전력의 미세한 조정도 가능해졌다. 핀펫 아키텍처로도 5나노 칩을 구현할 수 있지만 단순히 핀 사이 간격을 줄이는 것으로 추가적인 성능을 위한 전류 증가는 기대하기 힘들다.

김동표 기자 letmein@asiae.co.kr

<ⓒ투자가를 위한 경제콘텐츠 플랫폼, 아시아경제(www.asiae.co.kr) 무단전재 배포금지>

![전문가 4인이 말하는 '의료 생태계의 대전환'[비대면진료의 미래⑥]](https://cwcontent.asiae.co.kr/asiaresize/319/2026013014211022823_1769750471.png)

![일주일 만에 2만원에서 4만원으로 '껑충'…머스크 언급에 기대감 커진 한화솔루션[이주의 관.종]](https://cwcontent.asiae.co.kr/asiaresize/308/2026021109215637724_1770769315.jpg)