카이스트·나노종합기술원 공동 개발, 단일 트랜지스터보다 5배 성능 높아져

[아시아경제 정종오 기자] 5단 수직 적층 반도체 트랜지스터가 개발됐다. 단일 나노선 기반의 트랜지스터보다 5배의 향상된 성능을 보였다.

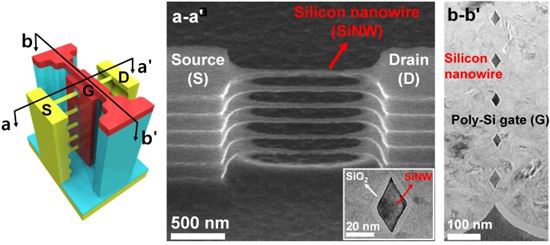

카이스트(KAIST, 총장 강성모) 전기 및 전자공학부 이병현 연구원(지도교수 최양규)과 나노종합기술원(원장 이재영) 강민호 박사가 실리콘 기반의 5단 수직 적층 반도체 트랜지스터를 내놓았다. 반도체 트랜지스터를 이용한 비휘발성 메모리 개발에 성공했다.

반도체 트랜지스터 분야는 모든 전자기기의 핵심 구성요소이다. 국내 산업과 경제 발전에 큰 영향을 끼친다. 세계적 추세에 따라 치열한 소형화를 통해 생산성과 성능의 향상을 거듭했다. 최근 10나노미터 시대에 접어들며 제작 공정의 한계와 누설전류로 인한 전력소모 문제가 커지고 있다.

학계와 산업계는 문제 해결을 위해 전면-게이트 실리콘 나노선 구조를 개발했다. 이는 누설전류 제어에 가장 효과적인 구조로 저전력 트랜지스터 개발에 이용됐다. 이 역시 소형화에 따른 나노선 면적 감소로 성능 저하의 한계가 있었다.

연구팀은 전면-게이트 실리콘 나노선을 수직으로 5단으로 쌓아 문제를 해결했다. 이 5단 적층 실리콘 나노선 채널을 보유한 반도체 트랜지스터는 단일 나노선 기반의 트랜지스터보다 5배의 향상된 성능을 보였다. 또 수직 적층 나노선 구조는 말 그대로 위로 쌓기 때문에 단일 구조와 달리 면적이 증가되지 않아 집적도 향상에도 기여할 수 있다.

나노선 수직 적층은 '일괄 플라즈마 건식 식각 공정' 방식을 통해 이뤄졌다. 이 공정은 고분자 중합체를 이용해 패턴이 형성될 영역에 미리 보호막을 친 뒤 등방성 건식 식각을 통해 나노선 구조를 형성하는 기술이다. 수직 적층 나노선 구조는 이 기술의 연속 작용을 통해 확보한 결과물이다.

이번 기술은 지속적 소형화로 인해 기술적 한계에 부딪힌 반도체 트랜지스터 분야에 새로운 돌파구를 제시할 것으로 기대된다.

정종오 기자 ikokid@asiae.co.kr

<ⓒ투자가를 위한 경제콘텐츠 플랫폼, 아시아경제(www.asiae.co.kr) 무단전재 배포금지>

![전문가 4인이 말하는 '의료 생태계의 대전환'[비대면진료의 미래⑥]](https://cwcontent.asiae.co.kr/asiaresize/319/2026013014211022823_1769750471.png)

![오입금 된 비트코인 팔아 빚 갚고 유흥비 쓴 이용자…2021년 대법원 판단은[리걸 이슈체크]](https://cwcontent.asiae.co.kr/asiaresize/308/2026021014460536494_1770702365.jpg)