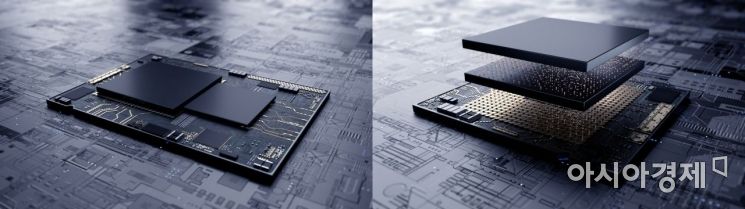

Samsung Electronics applies 3D stacking technology to cutting-edge EUV system semiconductors for the first time in the industry. On the left is the planar design of conventional system semiconductors. On the right is the design of system semiconductors with Samsung Electronics' 3D stacking technology 'X-Cube' applied.

Samsung Electronics applies 3D stacking technology to cutting-edge EUV system semiconductors for the first time in the industry. On the left is the planar design of conventional system semiconductors. On the right is the design of system semiconductors with Samsung Electronics' 3D stacking technology 'X-Cube' applied.

[Asia Economy Reporter Changhwan Lee] Samsung Electronics announced on the 13th that it has succeeded in producing a test chip applying the industry's first 7-nanometer extreme ultraviolet (EUV) system semiconductor with 3D stacked packaging technology called 'X-Cube'.

Samsung Electronics emphasized that it has secured advanced technological competitiveness not only in the cutting-edge EUV ultra-fine front-end process but also in the back-end process, and this is expected to play a significant role in achieving the 'Semiconductor Vision 2030'.

'X-Cube' is a technology that stacks multiple chips in a wafer state, after completing the front-end process, thinly on top of each other to create a single semiconductor.

System semiconductors are generally designed by placing the logic part, which performs roles such as CPU, GPU, and NPU, and the SRAM part, which acts as cache memory, side by side on a single chip in a planar layout.

Cache memory is a temporary storage space that stores frequently performed tasks or operations, enabling fast processing without passing through the main memory, DRAM.

The 'X-Cube' technology designs and produces logic and SRAM (Static Random Access Memory) separately and stacks them vertically, allowing for a reduction in the overall chip area while equipping high-capacity memory solutions, thereby increasing the customer's design freedom.

Additionally, through Through Silicon Via (TSV) technology, the data processing speed of system semiconductors can be dramatically improved, and power efficiency can also be enhanced.

TSV (Through Silicon Via) is a packaging technology that connects chips by drilling tiny holes in the chip and connecting the top and bottom chips with electrodes instead of using wires, significantly improving speed and power consumption.

Moreover, the data communication channels between the top and bottom chips can be freely expanded according to customer design, and the signal transmission path can also be minimized, maximizing data processing speed.

This technology is expected to be utilized as a core technology that can enhance competitiveness in fields requiring high-performance system semiconductors such as supercomputers, artificial intelligence (AI), and 5G, as well as smartphones and wearable devices.

Global fabless customers can immediately start developing 5- and 7-nanometer process chips based on EUV technology by utilizing Samsung Electronics' 'X-Cube' design methodology and design flow.

In particular, since they can use Samsung Electronics' already verified mass production infrastructure, they can quickly identify development errors and reduce chip development time.

Kang Moon-soo, Executive Vice President of the Market Strategy Team at Samsung Electronics' Foundry Business Division, said, "We have stably implemented TSV technology even in advanced processes applied with EUV equipment," and added, "Samsung Electronics will continue to innovate technologies to overcome semiconductor performance limits."

Meanwhile, Samsung Electronics plans to reveal the technological achievements of 'X-Cube' at 'Hot Chips 2020,' an annual academic event related to high-performance semiconductors, held online from the 16th to the 18th.

© The Asia Business Daily(www.asiae.co.kr). All rights reserved.

![Clutching a Stolen Dior Bag, Saying "I Hate Being Poor but Real"... The Grotesque Con of a "Human Knockoff" [Slate]](https://cwcontent.asiae.co.kr/asiaresize/183/2026021902243444107_1771435474.jpg)