KAIST, Northeastern University, Boston University, and University of Murcia Collaborate

Improving Performance in AI and Big Data Applications Based on PIM

Enhancing the Usability of PIM Systems

An international joint research team has solved the bottleneck problem caused by existing Processing-in-Memory (PIM) semiconductors having to communicate through an external central processing unit (CPU).

The Korea Advanced Institute of Science and Technology (KAIST) announced on the 19th that Professor Dongjun Kim's research team from the Department of Electrical Engineering collaborated with renowned researchers from Northeastern University, Boston University, and the University of Murcia in Spain to develop a method that dramatically improves the communication performance of PIM semiconductors through a "specialized interconnection network architecture for collective communication among PIM semiconductors."

Hyojun Son, Ph.D. candidate in the Department of Electrical Engineering at KAIST (left), Dongjun Kim, Professor. Provided by KAIST

Hyojun Son, Ph.D. candidate in the Department of Electrical Engineering at KAIST (left), Dongjun Kim, Professor. Provided by KAIST

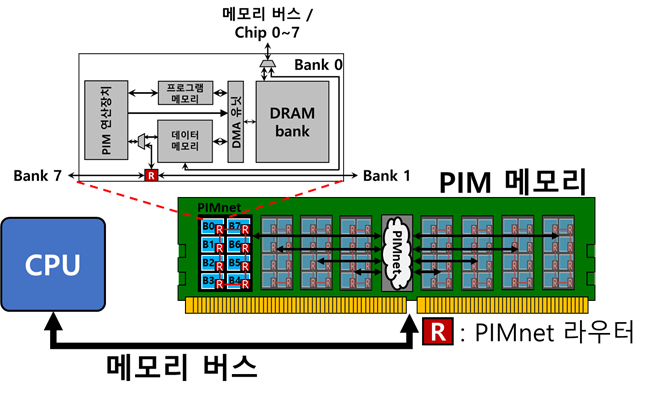

The research team identified the limitations of the communication structure among internal computing units within existing PIM semiconductors. They proposed a method to maximize the communication performance of PIM semiconductors by applying an "interconnection network structure" that directly connects each computing unit while making maximum use of the existing bus structure for data movement inside the memory.

Through this, they developed a specialized interconnection network structure for PIM semiconductors that minimizes CPU intervention for communication processing during PIM semiconductor computations, thereby enhancing the overall performance and usability of PIM semiconductor systems.

Conceptual diagram of communication between PIM processing units applying PIM-specialized interconnect. Provided by Professor Dongjun Kim's research team.

Conceptual diagram of communication between PIM processing units applying PIM-specialized interconnect. Provided by Professor Dongjun Kim's research team.

Existing PIM semiconductors suffered significant performance loss because communication had to go through the CPU. However, by applying the PIM-specialized interconnection network, application performance improves up to 11 times compared to existing systems. This is because it maximizes the utilization of internal memory bandwidth of PIM semiconductors and communication performance scalability increases as the scale of the PIM memory system grows.

Professor Kim, who led this research and was the first Korean to be appointed as an IEEE Fellow in the field of computer architecture in 2025 by the Institute of Electrical and Electronics Engineers (IEEE), explained, "Reducing data movement is a key factor in all system semiconductors, including PIM, and PIM can improve the performance and efficiency of computing systems. However, data movement among PIM computing units can limit performance scalability, restricting application areas. PIM interconnects can be a solution to this."

This research, with Hyojun Son, a Ph.D. candidate in the Department of Electrical Engineering at KAIST, as the first author, will be presented next month at HPCA 2025 (31st IEEE International Symposium on High Performance Computer Architecture), the top international conference in computer architecture, held in Las Vegas, Nevada, USA.

© The Asia Business Daily(www.asiae.co.kr). All rights reserved.

![Clutching a Stolen Dior Bag, Saying "I Hate Being Poor but Real"... The Grotesque Con of a "Human Knockoff" [Slate]](https://cwcontent.asiae.co.kr/asiaresize/183/2026021902243444107_1771435474.jpg)